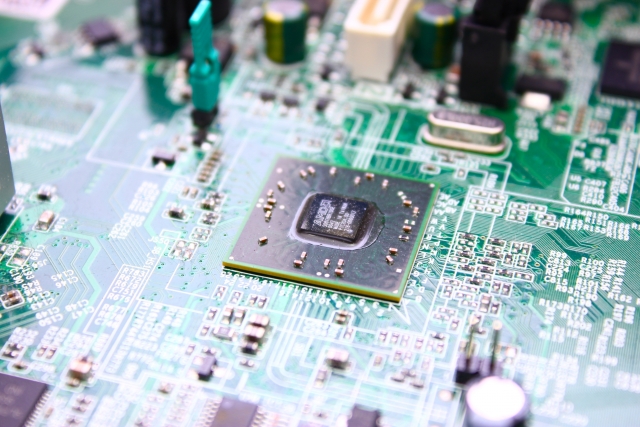

異種チップ集積は現在、2つの方向で技術開発が進んでいる。

1つは「先進2次元実装」です。これは平面に複数チップを並べて、

あたかも1つのチップのように扱う技術です。

ロジックチップ同士の接続や、プロセッサーとメモリーの接続で使用されています。

もう1つが「3次元実装」です。

これは複数チップを縦方向に積層する技術です。

現時点では、比較的熱を発生しにくいメモリーチップ間の接続や、

多段にならないメモリーとプロセッサーの接続、

CMOSイメージセンサーとロジックチップの接続など限られた用途での採用が進んでいます。

3次元実装は高速・低消費電力性に優れる反面、コストや放熱性という面で課題があります。

先進2次元実装はコストや放熱性に優れる一方、高速・低消費電力性で3次元実装より劣ります。

これらの欠点を補うべく技術開発が盛んに行われています。

例えば、3次元実装の最大の課題である放熱対策でも、下記を中心とした研究が進んでいます。

①薄膜化

②熱伝導性が優れた材質の開発

③積層チップの並べ方

④熱伝導性が優れた放熱機構の開発

放熱が多いプロセッサーを上に配置し、熱があまり出ないI/O等を下に配置する事で放熱対策をしている。

シリコン内に微細な穴を開け、液体を流すためのトンネル内に液体を流し込む事で熱を除去する機構。

サーテックは、最先端モノづくり屋さんとして、このような最先端技術支援をしています。

まずはお気軽にお問い合わせください。

E-mail: info@cir-tech.co.jp

TEL:053-522-9255